반도체 기억장치

RAM

특성:

임의 액세스 방식

반도체 직접회로 기억장치

데이터 읽기와 쓰기 모두 가능

휘발성 : 전원 공급이 중단되면 데이터 손실(컴퓨터 종료 등)

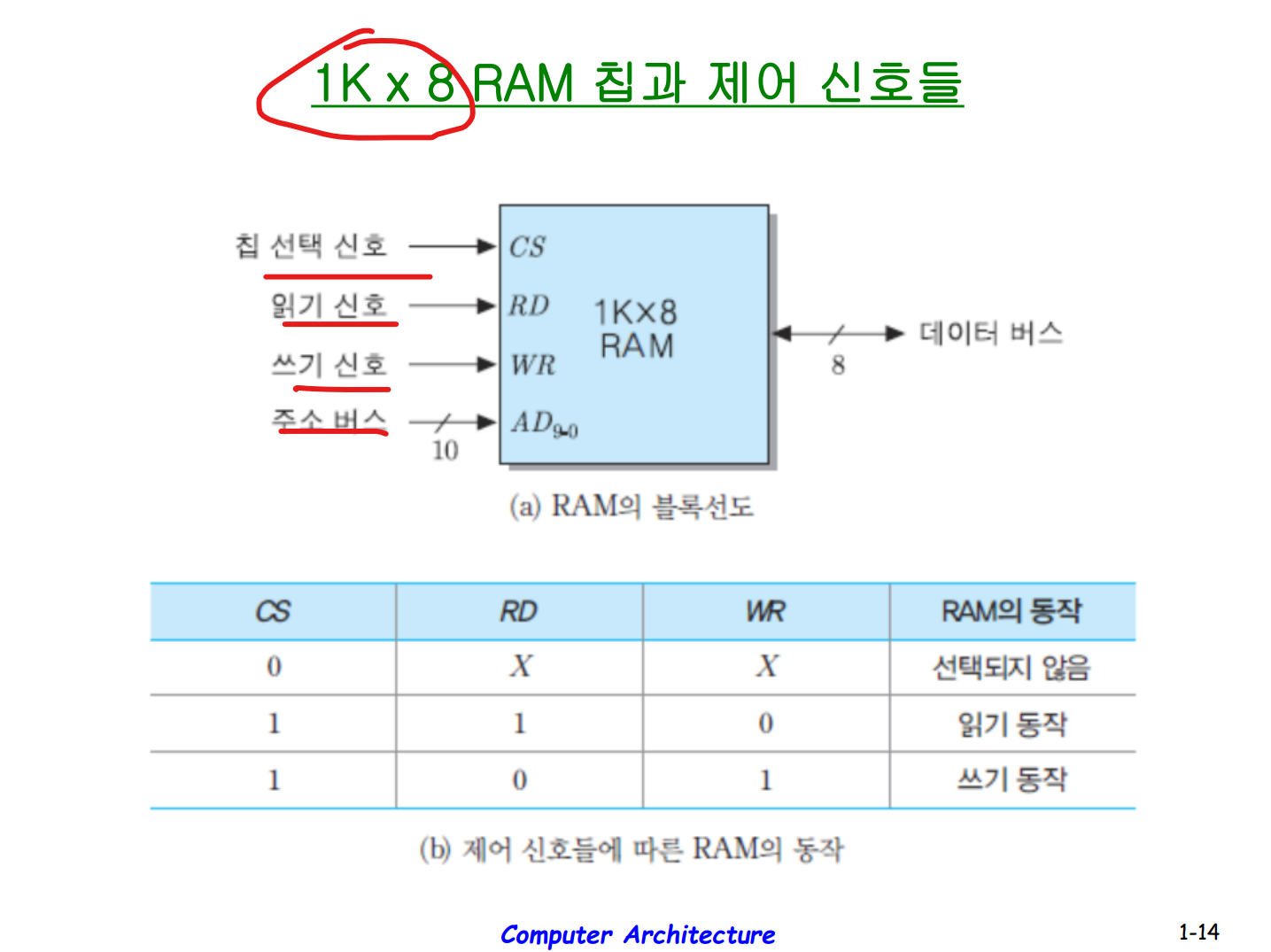

램의 구조

램의 구조입니다.

1편을 보고오면 알겠지만 1K*8이라 함은 2^10*8입니다. 즉 10은 방의 개수 입니다. 그렇기에 주소 버스는 10비트로 되있습니다. RAM은 주소버스 쓰기 신호 읽기 신호 칩 선택 신호로 구성이 되어있고 데이터 버스로 구성되어 있습니다.

데이터 버스는 2^10*8이니 8비트가 됩니다.

칩 선택 신호는 CS라고 하는데요. CS가 0으로 셋팅된다면 읽기 쓰기 모두 X

1이 들어온다면 읽기만 가능. CS가 0이면 쓰기만 가능 합니다.

램의 종류

램은 DRAM과 SRAM으로 구성되어 있습니다.

DRAM

DRAM은 흔히 사람들이 별명으로 D..똥 램이라 합니다 그 이유는

데이터의 저장상태를 유지하기 위하여 "재충전"을 해야만 합니다.

같은 용량의 SRAM보다 가격이 더 싸며 용량이 큰 주기억장치로 사용 됩니다.

SRAM

SRAM은 S를 따서 Speed RAM이라 합니다.

DRAM보다 속도가 빠르며 재충전 없이도 데이터를 계속 유지하는게 가능합니다.

또한 높은 속도가 필요한 캐시메모리로 사용됩니다.

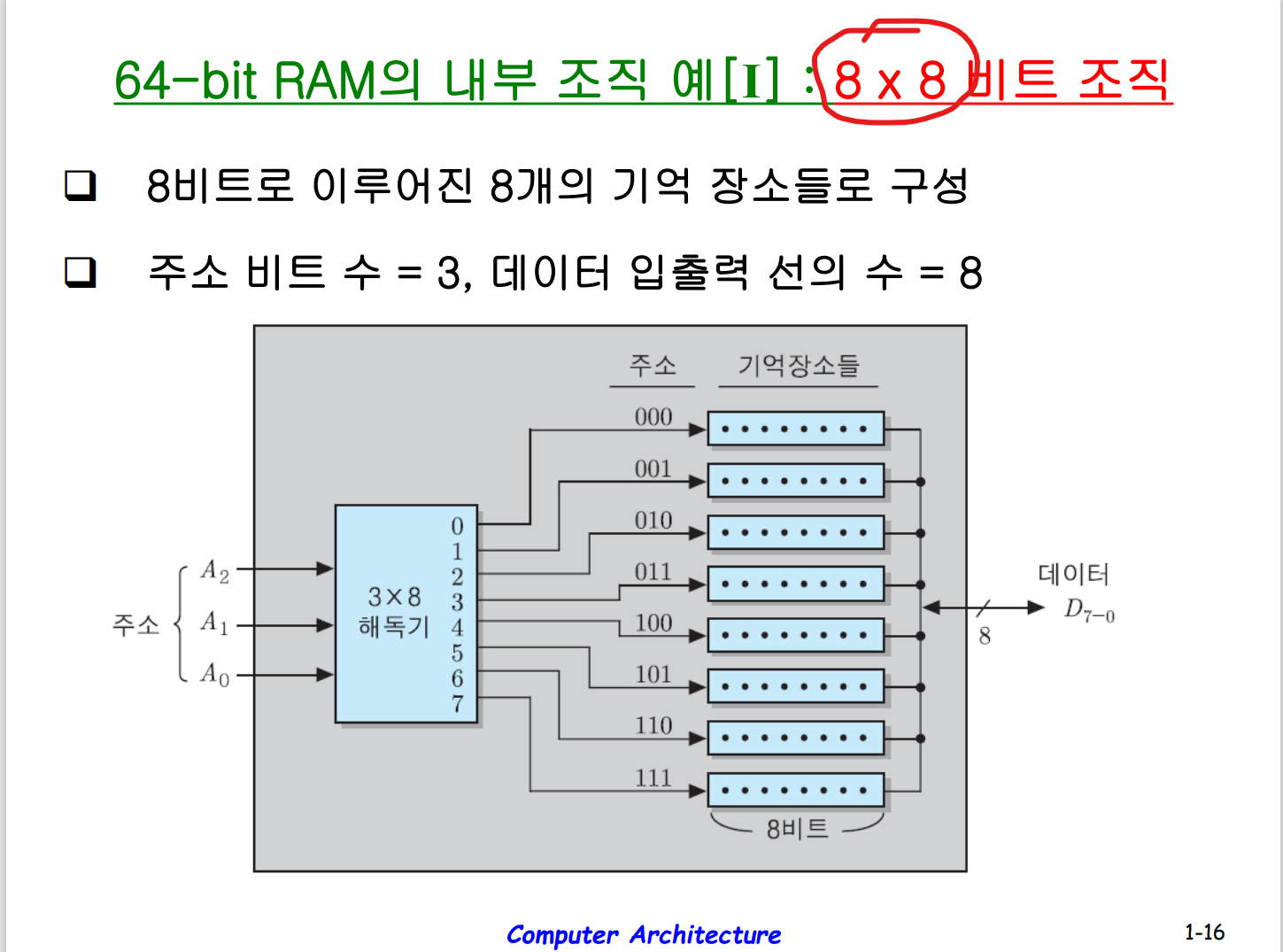

또한 64비트의 메모리 내부 구조입니다.

해독기 부분을 보면 3*8이 있습니다. 이건 위에 말했다 싶이 3은 방의 개수 이며 8은 방의 크기입니다.

그렇기에 2^3임으로 방의 개수는 8개 비트는 8비트로 구성이 되어있습니다.

그렇기에 만약 비트로 나타낸다면 첫 번째 주소는 0000 0000 두번째 주소는 0000 0001이 되겠습니다.

다음 진도를 나가기전에 한번 풀고 가시는걸 추천 드립니다.

답지는 스크랩 하시면 있습니다.

첫번째 문제인 경우는 1K*8=2^10*8임으로 주소는 10비트가 필요하다.

두번째 문제인 경우는 128K*8=1Mbits는 2^20입니다.

하지만 128은 2^7이죠? 1M는 2^10이기 때문에 10+7=17비트가 필요합니다.

세번째인 경우 1Gbits로 구한다면 2^30

128M*8이니까

128은 2^7+20=27비트가 필요합니다.

그렇다면 이 내부구조도 저희는 이제 쉽게 해석할 수 있습니다.

16*4라고 되어있네요 64비트니까 16으로 나눌시 64가 될려면 4가 필요하니 4로 나눴나 봅니다.

그렇다면 2^4*4 즉 방의 개수는 4개 데이터 크기는 4비트입니다.

한번 풀어보시는걸 추천드립니다.

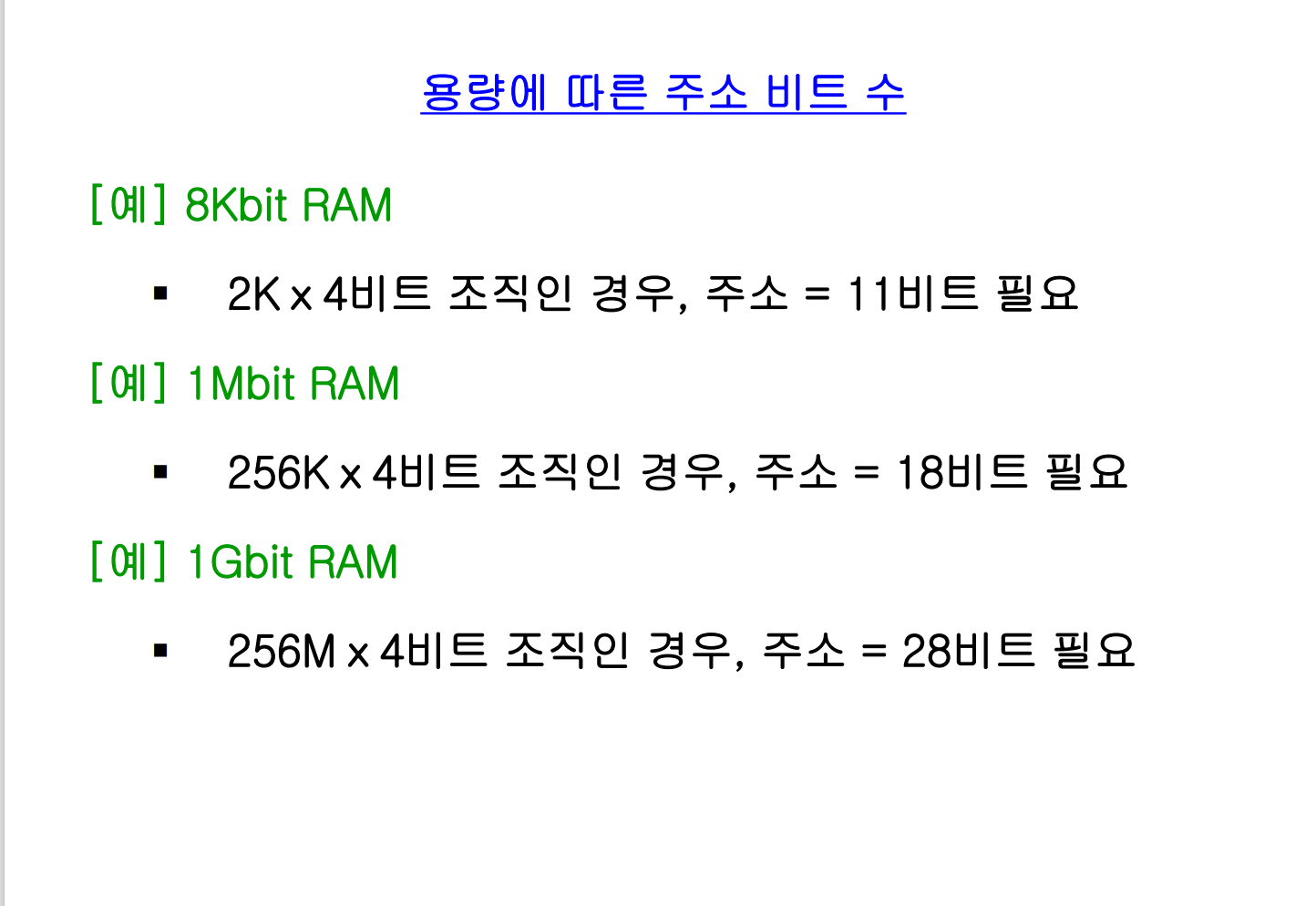

1.2K*4= 즉 1K는 2^10 2K는 1*2=2 즉 11비트가 필요합니다.

2. 256K 2^10+2^8= 18비트 필요

3. 256 2^20+2^8=28비트필요

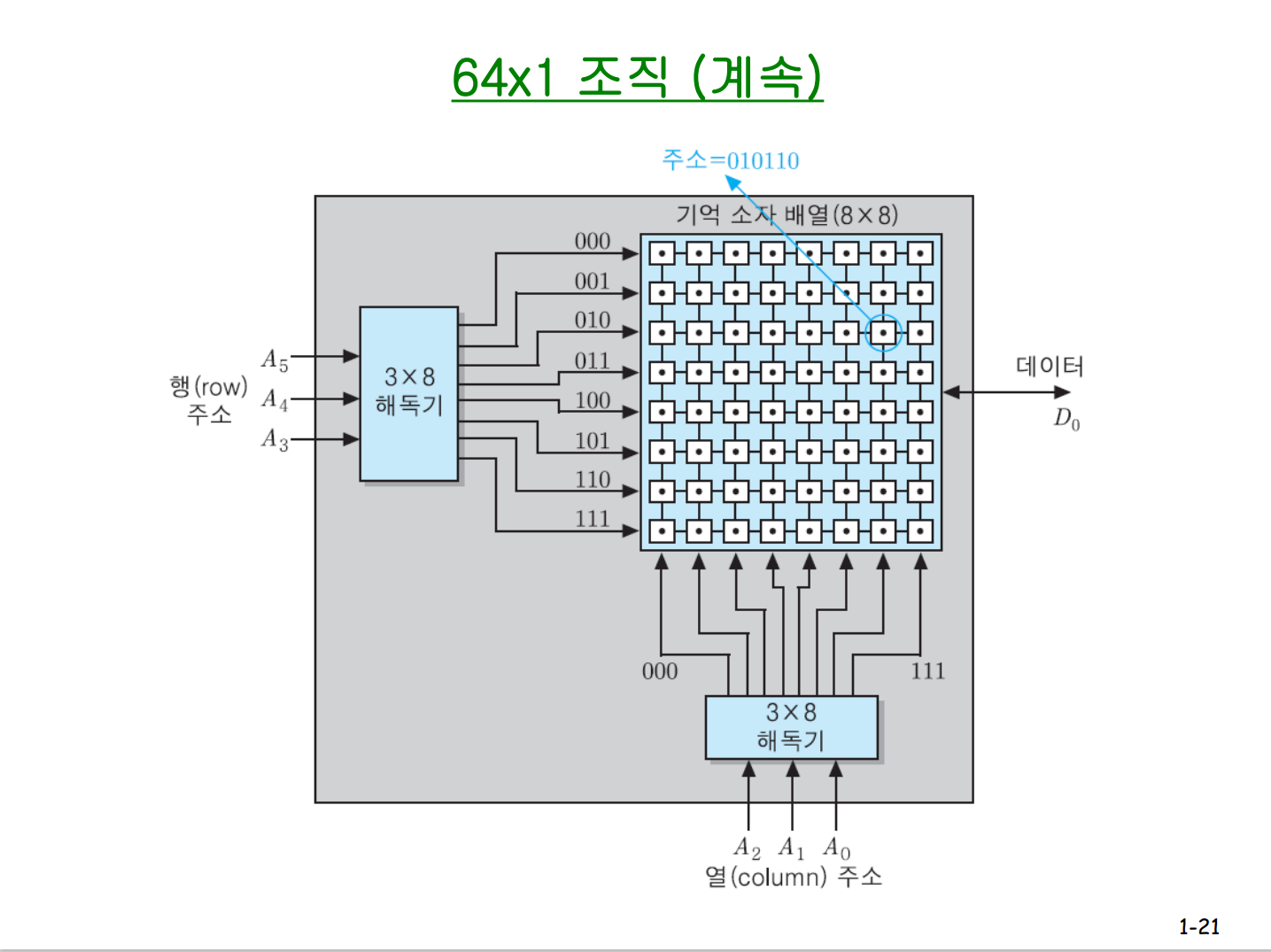

이제는 1비트 크기로 64개의 방을 나눴습니다.

이 RAM은 병렬구조로 되어있습니다. 64비트는 2^6으로 6개의 주소비트를 필요로 합니다.

그렇기에

총 6개의 주소비트로 되어있으니 행의 주소로 3비트를 보내주고

열의 비트로 3의 비트를 전송 해주었습니다. 그렇게 010 110 = 010110의 주소비트가 완성되었습니다.

이제는 쉽게 푸실 수 있다고 생각합니다.

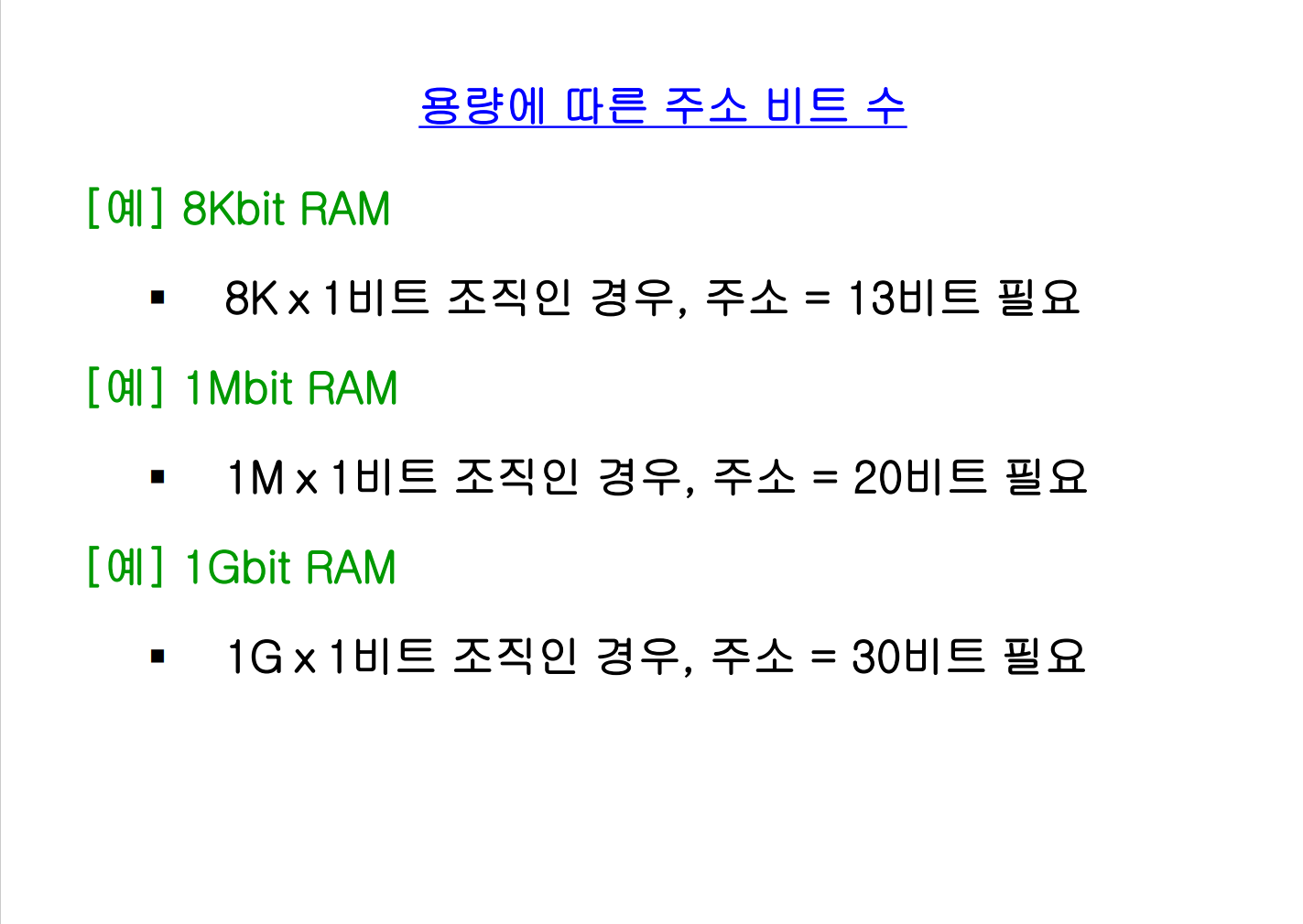

1.8K는 2^3+2^10=13비트 필요

2.1M= 2^20 = 20비트필요

3. 1G = 2^30=30비트필요 1G=2^30(Bit)

'컴퓨터 구조론' 카테고리의 다른 글

| [컴퓨터구조론] 제어유니트 (2) | 2022.12.06 |

|---|---|

| [컴퓨터 구조 5장 3편] ROM과 캐쉬 메모리 (1) | 2022.12.04 |

| [컴퓨터구조론 5장 ]RAM의 역할과 RAM이 하는 일을 알아보자 (1) | 2022.12.04 |